# Three-Gigahertz Graphene Frequency Doubler on Quartz Operating Beyond the Transit Frequency

Michael E. Ramón, *Student Member, IEEE*, Kristen N. Parrish, *Student Member, IEEE*, Sk. Fahad Chowdhury, Carl W. Magnuson, Hema C. P. Movva, Rodney S. Ruoff, Sanjay K. Banerjee, *Fellow, IEEE*, and Deji Akinwande, *Member, IEEE*

Abstract—We demonstrate a 500-nm graphene frequency doubler with a record 3-GHz bandwidth, exceeding the device transit frequency by 50%, a previously unobserved result in graphene, indicating that graphene multiplier devices might be useful beyond their transit frequency. The maximum conversion gain of graphene ambipolar frequency doublers is determined to approach a near lossless value in the quantum capacitance limit. In addition, the experimental performance of graphene transistor frequency detectors is demonstrated, showing responsivity of 25.2  $\mu$ A/ $\mu$ W. The high-frequency performance of these gigahertz devices is enabled by top-gate device fabrication using synthesized graphene transferred onto low capacitance, atomically smooth quartz substrates, affording carrier mobilities as high as 5000 cm²/V·s.

Index Terms—Bandwidth, doubler, graphene, quartz, radio frequency devices, transit frequency.

#### I. INTRODUCTION

RAPHENE, a 2-D sheet of carbon atoms arranged in a honeycomb lattice [1], has attracted significant interest as a channel material for high-frequency analog electronics [2]–[14]. This can be attributed to its high-carrier mobility [15], large current densities [16], thermal and mechanical stability [17], [18] and intrinsic ambipolar electron—hole symmetry. A unique device application of its ambipolar property is for frequency translation where input signal frequencies can be translated up to higher frequencies (frequency multipliers) often in integer multiples or translated down to zero or baseband

Manuscript received December 16, 2011; revised February 17, 2012; accepted March 19, 2012. Date of publication June 8, 2012; date of current version September 1, 2012. This work was supported in part by NRI-SWAN, ONR, and in part by the DARPA Contract FA8650-08-C-7838 through the CERA program and IBM-UT Subcontract Agreement W0853811. The work of C. W. Magnuson was supported by the Laboratory Directed Research and Development program at Sandia National Laboratories. The review of this paper was arranged by Associate Editor R. Lake.

M. E. Ramón, K. N. Parrish, Sk. F. Chowdhury, H. C. P. Movva, S. K. Banerjee, and D. Akinwande are with the Microelectronics Research Center, The University of Texas at Austin, Austin, TX 78758 USA (e-mail: mramon@mail.utexas.edu; kparrish@utexas.edu; sk.chowdhury. fahad@gmail.com; hemacp@gmail.com; banerjee@ece.utexas.edu; deji@ece.utexas.edu).

C. W. Magnuson and R. S. Ruoff are with the Department of Mechanical Engineering and the Materials Science and Engineering Program, The University of Texas at Austin, Austin, TX 78712 USA (e-mail: carl.magnuson@mail.utexas.edu; r.ruoff@mail.utexas.edu).

This paper has supplementary downloadable material available at http://ieeexplore.ieee.org

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TNANO.2012.2203826

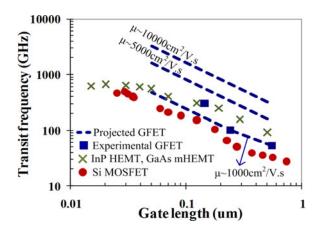

Fig. 1. Transit frequency comparison for different high-frequency FETs versus gate length. The symbols are experimental data points and the dashed lines are the projected mobility-scaled performance of GFETs. 300 GHz  $f_t$  is the fastest experimental GFET to date [10]. For terahertz operation, higher mobility scaled GFETs (dashed lines) offer the greatest prospects at moderate gate lengths. Figure adapted from Schwierz [11]. THz  $f_t$  values are also confirmed by quantum mechanical simulations that include velocity saturation [20].

frequencies (frequency detectors) [2]–[5]. In recent years, frequency multipliers have received renewed attention particularly for terahertz (~100 GHz–1 THz) applications driven by strategic interests in security, imaging, short-range communication, and molecular spectroscopy [19].

Graphene field-effect transistors (GFETs) appear to be the most promising transistor device for terahertz applications owing to their high mobility which yields the highest cutoff or transit frequencies beyond the reach of conventional solid-state transistors as shown in Fig. 1. In this paper, we demonstrate for the first time a GFET operating  $\sim 50\%$  beyond its transit frequency  $f_t$ . This previously unobserved result indicates that graphene devices employing the ambipolar property might be even more useful for high-frequency electronics than previously thought, potentially providing useful electronic performance beyond the experimental 300 GHz and predicted terahertz device transit frequencies [10], [20].

The fabricated GFET with 500-nm channel length and biased at the Dirac point for frequency doubling achieves a maximum output power of approx. -23.3 dBm and record bandwidth of 3 GHz,  $2\times$  higher than the state-of-the-art GFET frequency doubler [2]. The 3-GHz frequency bandwidth exceeds the measured 2-GHz device  $f_t$  by 50%, a new achievement for graphene devices. Operation beyond  $f_t$  is not entirely unexpected since the graphene frequency multiplier offers no gain. Nonetheless, this is the first experimental observation of graphene circuit

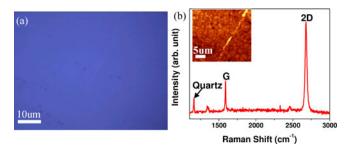

Fig. 2. (a) Optical image of graphene on quartz showing an even color indicative of uniform coverage. (b) Raman spectroscopy of the CVD grown graphene used in this work confirming the monolayer structure. *Inset*: Local Raman map of the unique monolayer 2-D peak showing uniform graphene coverage over  $700 \, \mu \text{m}^2$  area that enabled the fabrication of arrays of devices.

bandwidth exceeding the device transit frequency. The 3-GHz multiplier bandwidth is afforded by transferring CVD-grown graphene onto low capacitance, atomically smooth quartz substrates which is an ideal choice for low loss and temperature stable high-frequency electronics [21]. GFET carrier mobilities as high as ~5000 cm²/V·s were observed, but can be as low as ~500 cm²/V·s due to the resist residue of current solution-based transfer methods which lead to uncontrolled impurity and defect scattering [22], [23] as indicated by a relatively flat mobility–temperature profile [24], [25]. We have included supplementary downloadable material, which includes temperature dependent mobility data. Remarkably, even with a low mobility GFET, record gigahertz performance is achieved.

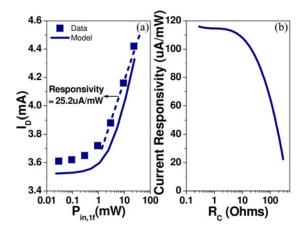

Furthermore, we address the most pressing question regarding the maximum conversion gain of GFET ambipolar frequency multipliers, uncovering an upper limit of near lossless frequency doubling in the quantum capacitance limit. In addition, the experimental performance of GFET frequency detectors was evaluated, showing current responsivity ( $\Delta I_D/\Delta P_{\rm in}$ ) of  $\sim\!25.2~\mu$ A/mW. The results reported here collectively indicate that optimized GFETs can enable high performance GHz and future terahertz systems via frequency translation and processing, an area of growing significance.

# II. DEVICE FABRICATION AND PERFORMANCE

## A. Graphene Synthesis

Large-area graphene films were synthesized on Cu substrates using a low-pressure CVD process as in [26]. After growth, the graphene was transferred to a single-crystal ST-cut quartz wafer by the process described in [27]. Fig. 2(a) shows an optical image of the monolayer graphene that has been transferred onto quartz, where the even color is indicative of uniform graphene coverage. As shown in Fig. 2(b), the Raman spectrum of the transferred graphene reveals a 2D peak at 2679 cm<sup>-1</sup> with a full width at half maximum (FWHM)  $\sim$ 24.5 cm<sup>-1</sup>, indicating monolayer graphene [28]–[30]. A peak at  $\sim$ 1160 cm<sup>-1</sup>, due to the quartz substrate, is also observed [31]. The inset of Fig. 2(b) shows the Raman mapping corresponding to the intensity of the 2-D peak, which further validates the uniformity of the graphene film over a 700  $\mu$ m<sup>2</sup> area, enabling the fabrication of arrays of devices.

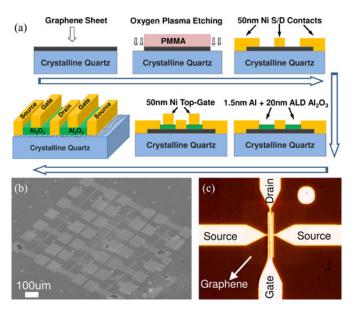

Fig. 3. (a) Illustration of top-gated graphene device fabrication process. (b) SEM image of a completed  $3 \times 3$  array of GFETs fabricated with the process illustrated in (a). (c) Optical image of a typical GFET from the  $3 \times 3$  array with an arrow indicating the location of a patterned graphene sheet underneath the active device region.

## B. Graphene Transistor Fabrication

GFETs were fabricated as illustrated in Fig. 3(a) using electron-beam lithography (EBL) and standard cleanroom processes. Charging effects of the insulating quartz substrate during EBL processing were avoided by using a water-soluble conducting polymer (Espacer 300Z from Showa Denko K.K.). After transfer of the graphene to the quartz substrate, an active region was defined by EBL and oxygen plasma etching. A second EBL step was performed to define metal contacts for the source and drain of a ground-signal-ground (GSG) structure, followed by a 50-nm thick Ni e-beam evaporation and lift-off process. The gate dielectric consists of a 1.5-nm thick Al nucleation layer, followed by a 20-nm thick Al<sub>2</sub>O<sub>3</sub> layer deposited by atomic layer deposition (ALD) [32]. A 50-nm thick Ni gate contact is then defined by EBL and a lift-off process. Fig. 3(b) shows a scanning electron microscope (SEM) image of a completed  $3 \times 3$  array of GFETs fabricated by the process illustrated in Fig. 3(a), and Fig. 3(c) shows an optical microscope image of a typical GFET. The arrow indicates the location of the patterned graphene sheet underneath the active device region. DC and RF characterizations were performed using an Agilent Semiconductor Device Analyzer and Microwave Network Analyzer, respectively.

#### C. Device Performance

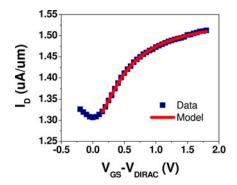

A representative transfer curve of a high-performance GFET on quartz is shown in Fig. 4 with extracted electron mobility of  $\sim 5000~\text{cm}^2/\text{V}\cdot\text{s}$ , using a well-established low-field diffusive transport model [32], [33]. The high-mobility suggests electrically good quality graphene that is not substantially impacted by the complex device fabrication. The output characteristics of a GFET for frequency multiplication is shown in

Fig. 4. Transfer curve of a GFET on quartz with 280 nm channel length. The electron mobility is  $\sim\!5000~\text{cm}^2/\text{V}\cdot\text{s}$  at room temperature in air extracted from a well-established low-field diffusive transport model [32], [33] ( $V_{\rm DS}=10~\text{mV}$ ).

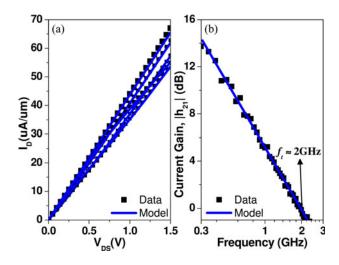

Fig. 5(a), in good agreement with a circuit model based on validated graphene compact models [34], [35]. The short circuit current gain  $|h_{21}|$  of a  $\sim 500 \text{ cm}^2/\text{V} \cdot \text{s}$  mobility GFET is shown in Fig. 5(b). The device transit frequency  $f_t$ , including the effects of all capacitances and contact resistance  $R_c$ , was directly measured to be 2 GHz at the peak electron transconductance ( $g_m$  $\sim 13.4 \,\mu\text{S}/\mu\text{m}$  at  $V_{\rm GS} \sim 2 \,\text{V}$ ) with  $V_{\rm DS} = 2.5 \,\text{V}$ . The transit frequency can also be calculated as  $f_t = g_m/(2\pi C_{\rm ox})$  [3], [7], [11], where the gate oxide capacitance  $C_{\rm ox}$  is  $\sim$ 190 nF/cm<sup>2</sup>, based on the transistor dimensions ( $W/L = 50 \,\mu\text{m}/0.5 \,\mu\text{m}$ ) and the gate dielectric stack [7], [36]. Using this equation,  $f_t$  is calculated to be ~2.25 GHz, in close agreement with the measured value, indicating the weak effect of parasitic substrate and fringe capacitances, a direct benefit of using insulating quartz for high-frequency applications. Mobility improvements via robust nondetrimental graphene postgrowth transfer will proportionately increase the device speed. For example, a mobility of 10 000 cm<sup>2</sup>/V·s for the given GFET will result in an  $f_t$  $\sim$ 40 GHz. This is remarkable because of the high extrinsic  $f_t$ which is actually accessible for circuits, in contrast to the often reported intrinsic  $f_t$  which is an idealized metric. The maximum oscillation frequency  $f_{\text{max}}$  was also measured (not shown) to be  $\sim$ 1.8 GHz.

# III. GFET Frequency Doubler

## A. Experimental Performance

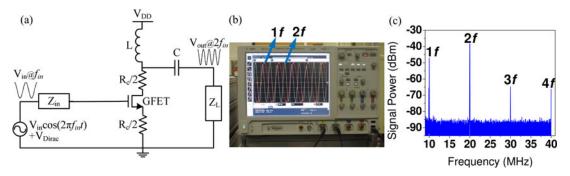

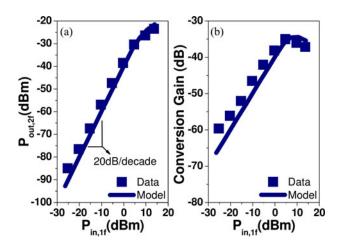

Fig. 6(a) shows the circuit schematic of a GFET frequency doubler, and Fig. 6(b) is the oscilloscope display, with clear evidence that the output (2 MHz) is oscillating at twice the input frequency (1 MHz). The device is biased at the Dirac point for maximum frequency doubling based on the intrinsic electronhole symmetry [2]–[5]. The spectrum analyzer output shown in Fig. 6(c) confirms frequency doubling for an input frequency of 10 MHz and also illustrates the high spectral purity of the output signal for the GFET doubler, where more than 90% of the output power is at the doubled frequency. All other harmonics are  $\geq 10 \times$  lower. Fig. 7(a) shows the output power of the doubled signal with a measured small-signal slope  $\sim 20$  dB/decade, as expected of ideal square-law ambipolar devices. Fig. 7(b) is the conversion gain  $(P_{\text{out},2f}/P_{\text{in},1f})$ , where  $P_{\text{in},1f}$  and  $P_{\text{out},2f}$  are

Fig. 5. (a) Output characteristics of the GFET multiplier in good agreement with a compact model based on prior work [34], [35].  $V_{\rm GS}$  varies from 0–2 V in 0.5 V steps. The validated compact model including nonidealities enables device and circuit performance assessment. (b) Measurement of the current gain of the GFET multiplier. The measured  $f_t$  is  $\sim$ 2 GHz including all the device intrinsic and extrinsic capacitances ( $V_{\rm DS}=2.5$  V and  $W/L=50~\mu{\rm m}/0.5~\mu{\rm m}$ ).

the input and output powers at the fundamental and doubled frequency, respectively) of the GFET frequency doubler. Both the output power and conversion gain are in strong agreement with the compact circuit model, revealing up to -23 dBm of available power.

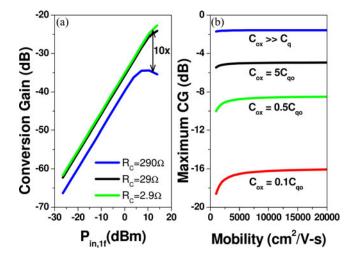

A primary metric for analog circuits is the -3-dB frequency  $(f_{-3\mathrm{dB}})$ , which represents the actual frequency bandwidth in practical circuit implementations. The GFET doubler's frequency response presented in Fig. 8 reveals  $f_{-3\mathrm{dB}}=3$  GHz, the highest bandwidth achieved for GFET frequency multipliers. The bandwidth, presently limited by low mobilities and contact resistance is expected to be at least  $10\times$  higher in the intrinsic limit based on reports of a similar experimental GFET with 500-nm channel length [7].

### B. Maximum Theoretical Conversion Gain

The conversion gain and output power of the GFET frequency doubler are presently limited by  $R_c$ , which is extracted to be  $\sim$ 290  $\Omega$ , on the order of the channel resistance at the Dirac point ( $R_{\rm Dirac} = 317 \,\Omega$ ). The same graphene transistor with negligible contact resistance can provide a 10× improvement in the conversion gain [see Fig. 9(a)]. We employ our validated circuit model to determine the maximum conversion gain achievable, currently the most pressing question related to graphene ambipolar frequency multipliers. In the theoretical limit of an ideal GFET with: 1) vanishing  $R_c$  and impurity carriers, 2) perfect electron-hole symmetry, and 3) saturation velocity bounded by the Fermi velocity ( $\sim 10^8$  cm/s), the maximum conversion gain approaches a near lossless ( $\sim$ -1.5 dB) performance as the gate oxide capacitance  $C_{ox}$  is scaled into the quantum capacitance  $C_q$  regime  $(C_{\text{ox}} \gg C_q)$  as shown in Fig. 9(b). This indicates that a 1000× improvement is possible compared to existing

Fig. 6. (a) Circuit schematic of the GFET frequency doubler,  $Z_{\rm in}=Z_L=50~\Omega$ , typical of gigahertz and terahertz systems. For maximum frequency doubling based on electron-hole symmetry, the device is biased at the Dirac point. The L and C network are necessary to route the dc and ac signals separately at the output. (b) Real-time oscilloscope output showing GFET frequency doubling at 2 MHz. (c) Spectrum analyzer output with 10 MHz input frequency and 0 dBm power. More than 90% of the output power is at the doubled frequency. All other harmonics are more than  $10 \times 10^{-1}$  lower than the doubled signal.

Fig. 7. (a) Doubled output power and (b) conversion gain of the experimental GFET frequency doubler with good agreement to graphene circuit model. The small-signal slope is 20 dB/decade expected of ideal square-law ambipolar devices. The GFET is biased at  $V_{\rm DIRAC}=1.4\,{\rm V}$  and  $V_{\rm DS}=2\,{\rm V}$ . The input frequency is 10 MHz and device  $W/L=50\,{\rm \mu m}/0.5\,{\rm \mu m}$ .

Fig. 8. Measured frequency response of the normalized conversion gain (CG) of the GFET frequency doubler. The straight line is the standard Bode guide for extracting the bandwidth. The extracted bandwidth is 3 GHz, a record bandwidth for GFET frequency multipliers. The GFET is biased at  $V_{\rm DIR\,AC}=1.4~{\rm V}$  and  $V_{\rm DS}=2~{\rm V}$  and device  $W/L=50~{\rm \mu m}/0.5~{\rm \mu m}$ .

experimental achievements in  $50 \Omega$  systems, and motivates the need for significant further device research and fabrication optimization. To place these results in perspective, the near lossless frequency doubling is  $>2 \times$  higher than an ideal varistor dou-

Fig. 9. (a) The simulated impact of  $R_c$  on the conversion gain of the experimental GFET frequency doubler. Circuit simulations indicate about  $10\times$  improvement in the maximum conversion gain if  $R_c$  were negligible compared to the channel resistance. For the experimental GFET,  $R_c \sim 290~\Omega$  and the channel resistance is  $\sim 317~\Omega$ . (b) Circuit simulations of the maximum conversion gain of an ideal GFET frequency doubler with scaled mobility and oxide capacitance revealing near lossless conversion gain in the quantum capacitance limit ( $C_{\rm ox} \gg C_q$ ).  $C_{\rm qo}~(\sim 8.4~{\rm fF}/\mu{\rm m}^2)$  is graphene's equilibrium quantum capacitance, a useful reference for normalizing  $C_{\rm ox}$ .

bler, and comparable to an ideal varactor doubler, albeit without the inherent narrowband limitation of varactors.

#### IV. EXPERIMENTAL GFET DETECTOR RESPONSIVITY

The current responsivity ( $\Delta I_D/\Delta P_{\mathrm{in},1f}$ ) or sensitivity of the GFET to input RF signals is reported in Fig. 10(a). The responsivity, a key metric for frequency detector and direct-conversion wireless receivers is measured to be  $\sim 25.2 \,\mu\text{A/mW}$ . Simulated removal of  $R_c$  results in  $>5\times$  improvement of the responsivity [see Fig. 10(b)].

Fig. 10. (a) Experimental GFET detector responsivity  $(\Delta I_D/\Delta P_{\mathrm{in},1f})$  measured for the first time. The input frequency is 10 MHz and the GFET is biased at the Dirac point for maximum rectification of ac signals. The dashed line is a visual guide. (b) Circuit simulation of the performance benefits available by minimizing contact resistance. The responsivity improves by more than  $5\times$  by scaling down  $R_c$  from 290  $\Omega$  to values much smaller than the channel resistance ( $\sim$ 317  $\Omega$ ).

### V. CONCLUSION

In summary, a record 3-GHz experimental graphene frequency doubler employing the intrinsic electron-hole symmetry has been reported on low capacitance, smooth crystalline quartz substrates. The 3-GHz operating bandwidth exceeds the device  $f_t$  by 50%, indicating that graphene multiplier circuits can substantially exceed the device transit frequency. In the limit of vanishing device nonidealities, we uncovered that near lossless frequency multiplication is possible, making optimized GFETs an attractive device for frequency multiplication at sub-THz frequencies beyond the frequency capability of conventional solid-state FETs.

## ACKNOWLEDGMENT

We thank S. Kim and E. Tutuc for useful discussions. Fabrication and characterization was performed at the Microelectronics Research Center (MER) and the Center for Nano and Molecular Science and Technology (CNM) at the University of Texas at Austin.

#### REFERENCES

- [1] A. K. Geim and K. S. Novoselov, "The rise of graphene," *Nat. Mater.*, vol. 6, pp. 183–191, Mar. 2007.

- [2] H. Wang, A. Hsu, K. K. Kim, J. Kong, and T. Palacios, "Gigahertz ambipolar frequency multiplier based on CVD graphene," in *Proc. IEEE Int. Electron Devices Meet.*, Tech Dig., 2010, pp. 23.6.1–23.6.4.

- [3] T. Palacios, A. Hsu, and H. Wang, "Applications of graphene devices in RF communications," *IEEE Commun. Mag.*, vol. 48, no. 6, pp. 122–128, Jun. 2010.

- [4] Z. Wang, Z. Zhang, H. Xu, L. Ding, S. Wang, and L.-M. Peng, "A high-performance top-gate graphene field-effect transistor based frequency doubler," *Appl. Phys. Lett.*, vol. 96, pp. 173104-1–173104-3, 2010.

- [5] L. Liao, J. Bai, R. Cheng, H. Zhou, L. Liu, Y. Liu, Y. Huang, and X. Duan, "Scalable fabrication of self-aligned graphene transistors and circuits on glass," *Nano Lett.*, vol. 12, no. 6, pp. 2653–2657, 2012.

- [6] Ph. Avouris, Y.-M. Lin, F. Xia, D. B. Farmer, Y. Wu, T. Mueller, K. Jenkins, C. Dimitrakopoulos, and A. Grill, "Graphene-based fast electronics and

- optoelectronics," in *Proc. IEEE Int. Electron. Devices Meet., Tech. Dig.*, 2010, pp. 23.1.1–23.1.4.

- [7] Y.-M. Lin, C. Dimitrakopoulos, K. A. Jenkins, D. B. Farmer, H.-Y. Chiu, A. Grill, and Ph. Avouris, "100-GHz transistors from wafer-scale epitaxial graphene," *Science*, vol. 327, p. 662, 2010.

- [8] I. Meric, N. Baklitskaya, P. Kim, and K. L. Shepard, "RF performance of top-gated, zero-bandgap graphene field-effect transistors," in *Proc. IEEE Int. Electron Devices Meet.*, Tech. Dig., 2008, pp. 1–4.

- [9] J. S. Moon, D. Curtis, M. Hu, D. Wong, C. McGuire, P. M. Campbell, G. Jernigan, J. L. Tedesco, B. VanMil, R. Myers-Ward, C. Eddy, Jr., and D. K. Gaskill, "Epitaxial-graphene RF field-effect transistors on Si-face 6 H-SiC substrates," *IEEE Electron Device Lett.*, vol. 30, no. 6, pp. 650– 652, Jun. 2009.

- [10] L. Liao, Y.-C. Lin, M. Bao, R. Cheng, J. Bai, Y. Liu, Y. Qu, K. L. Wang, Y. Huang, and X. Duan, "High-speed graphene transistors with a selfaligned nanowire gate," *Nature*, vol. 467, pp. 305–308, 2010.

- [11] F. Schwierz, "Graphene transistors," Nat. Nanotechnol., vol. 5, pp. 487–496, Jul. 2010.

- [12] M. Dragoman, D. Neculoiu, G. Deligeorgis, G. Konstantinidis, D. Dragoman, A. Cismaru, A. A. Muller, and R. Plana, "Millimeter-wave generation via frequency multiplication in graphene," *Appl. Phys. Lett.*, vol. 97, pp. 093101-1–093101-3, 2010.

- [13] X. Yang, G. Liu, A. A. Balandin, and K. Mohanram, "Triple-mode single-transistor graphene amplifier and its applications," ACS Nano, vol. 4, no. 10, pp. 5532–5538, 2010.

- [14] X. Yang, G. Liu, M. Rostami, A. A. Balandin, and K. Mohanram, "Graphene ambipolar multiplier phase detector," *IEEE Electron Device Lett.*, vol. 32, no. 10, pp. 1328–1330, Oct. 2011.

- [15] K. I. Bolotin, K. J. Sikes, Z. Jiang, M. Klima, G. Fundenberg, J. Hone, P. Kim, and H. L. Stormer, "Ultrahigh electron mobility in suspended graphene," *Solid State Commun.*, vol. 146, pp. 351–355, 2008.

- [16] A. Barreiro, M. Lazzeri, J. Moser, F. Mauri, and A. Bachtold, "Transport properties of graphene in the high-current limit," *Phys. Rev. Lett.*, vol. 103, pp. 076601-1–076601-4, 2009.

- [17] T. J. Booth, P. Blake, R. R. Nair, D. Jiang, E. W. Hill, U. Bangert, A. Bleloch, M. Gass, K. S. Novoselov, M. I. Katsnelson, and A. K. Geim, "Macroscopic graphene membranes and their extraordinary stiffness," *Nano Lett.*, vol. 8, no. 8, pp. 2442–2446, 2008.

- [18] J. H. Seol, I. Jo, A. L. Moore, L. Lindsay, Z. H. Aitken, M. T. Pettes, X. Li, Z. Yao, R. Huang, D. Broido, N. Mingo, R. S. Ruoff, and L. Shi, "Twodimensional phonon transport in supported graphene," *Science*, vol. 328, pp. 213–216, 2010.

- [19] A. Scavennec, M. Sokolich, and Y. Baeyens, "Semiconductor technologies for higher frequencies," *IEEE Microw. Mag.*, vol. 10, no. 2, pp. 77–87, Apr. 2009.

- [20] J. Chauhan and J. Guo, "Assessment of high-frequency performance limits of graphene field-effect transistors," *Nano Res.*, vol. 4, no. 6, pp. 571–579, 2011.

- [21] D. Akinwande, Y. Nishi, and H.-S. P. Wong, "Carbon nanotube quantum capacitance for nonlinear terahertz circuits," *IEEE Trans. Nanotechnol.*, vol. 8, no. 1, pp. 31–36, Jan. 2009.

- [22] A. Pirkle, J. Chan, A. Venugopal, D. Hinojos, C. W. Magnuson, S. McDonnell, L. Colombo, E. M. Vogel, R. S. Ruoff, and R. M. Wallace, "The effect of chemical residues on the physical and electrical properties of chemical vapor deposited graphene transferred to SiO<sub>2</sub>," *Appl. Phys. Lett.*, vol. 99, pp. 122108-1–122108-3, 2011.

- [23] M. Ishigami, J. H. Chen, W. G. Cullen, M. S. Fuhrer, and E. D. Williams, "Atomic structure of graphene on SiO<sub>2</sub>," *Nano Lett.*, vol. 7, no. 6, pp. 1643–1648, 2007.

- [24] J.-H. Chen, C. Jang, S. Xiao, M. Ishigami, and M. S. Fuhrer, "Intrinsic and extrinsic performance limits of graphene devices on SiO<sub>2</sub>," *Nat. Nanotechnol.*, vol. 3, pp. 206–209, Apr. 2008.

- [25] B. Fallahazad, S. Kim, L. Colombo, and E. Tutuc, "Dielectric thickness dependence of carrier mobility in graphene with HfO<sub>2</sub> top dielectric," *Appl. Phys. Lett.*, vol. 97, pp. 123105-1–123105-3, 2010.

- [26] X. Li, C. W. Magnuson, A. Venugopal, R. M. Tromp, J. B. Hannon, E. M. Vogel, L. Colombo, and R. S. Ruoff, "Large-area graphene single crystals grown by low-pressure chemical vapor deposition of methane and copper," J. Am. Chem. Soc., vol. 133, pp. 2816–2819, 2011.

- [27] J. W. Suk, A. Kitt, C. W. Magnuson, Y. Hao, S. Ahmed, J. An, A. K. Swan, B. B. Goldberg, and R. S. Ruoff, "Transfer of CVD-grown monolayer graphene onto arbitrary substrates," *ACS Nano*, vol. 5, no. 9, pp. 6916–6924, 2011.

- [28] M. E. Ramón, A. Gupta, C. Corbet, D. A. Ferrer, H. C. P. Movva, G. Carpenter, L. Colombo, G. Bourianoff, M. Doczy, D. Akinwande,

- E. Tutuc, and S. K. Banerjee, "CMOS-compatible synthesis of large-area, high-mobility graphene by chemical vapor deposition of acetylene on cobalt thin films," *ACS Nano*, vol. 5, no. 9, pp. 7198–7204, 2011.

- [29] X. Li, W. Cai, J. An, S. Kim, J. Nah, D. Yang, R. Piner, A. Velamakanni, I. Jung, E. Tutuc, S. K. Banerjee, L. Colombo, and R. S. Ruoff, "Largearea synthesis of high-quality and uniform graphene films on copper foils," *Science*, vol. 324, pp. 1312–1314, Jun. 2009.

- [30] S. Lee, K. Lee, and Z. Zhong, "Wafer scale homogeneous bilayer graphene films by chemical vapor deposition," *Nano Lett.*, vol. 10, pp. 4702–4707, 2010.

- [31] R. S. Krishnan, "Raman spectrum of quartz," *Nature*, vol. 155, p. 452, Apr. 1945.

- [32] S. Kim, J. Nah, I. Jo, D. Shahrjerdi, L. Colombo, Z. Yao, E. Tutuc, and S. K. Banerjee, "Realization of a high mobility dual-gated graphene field-effect transistor with Al<sub>2</sub>O<sub>3</sub> dielectric," *Appl. Phys. Lett.*, vol. 94, pp. 062107-1–062107-3, 2009.

- [33] A. Venugopal, J. Chan, X. Li, C. W. Magnuson, W. P. Kirk, L. Colombo, R. S. Ruoff, and E. M. Vogel, "Effective mobility of single-layer graphene transistors as a function of channel dimensions," *J. Appl. Phys.*, vol. 109, pp. 104511-1–104511-5, 2011.

- [34] K. N. Parrish and D. Akinwande, "Impact of contact resistance on the transconductance and linearity of graphene transistors," *Appl. Phys. Lett.*, vol. 98, pp. 183505-1–183505-3, 2011.

- [35] S. A. Thiele, J. A. Schaefer, and F. Schwierz, "Modeling of graphene metal-oxide-semiconductor field-effect transistors with gapless large-area graphene channels," *J. Appl. Phys.*, vol. 107, pp. 094505-1–094505-8, 2010.

- [36] B. Fallahazad, K. Lee, S. Kim, C. Corbet, and E. Tutuc, "Gate capacitance scaling and graphene field-effect transistors with ultra-thin top-gate dielectrics," in *Proc. IEEE Device Res. Conf.*, Jun. 2011, pp. 35–36.

His research interests include graphene based field-effect transistors (FETs), including design and fabrication for high-frequency applications, graphene FET-based circuits, and graphene-Si CMOS integration.

Carl W. Magnuson received the B.S. degree in electrical engineering in 2005 from the University of Southern California in Los Angeles, Los Angeles. He is currently working toward the Ph.D. degree in materials science and engineering at the University of Texas at Austin, Austin.

After receiving the B.S. degree, he was at Northrop Grumman Corporation, Azusa, CA, for 3 years as a Systems Engineer on surveillance and remote sensing satellite systems. His research interests include graphene growth on copper via thermal low-pressure

chemical vapor deposition in Prof. R. S. Ruoff's research group at The University of Texas at Austin.

Mr. Magnuson received the Laboratory Directed Research and Development Fellowship by Sandia National Laboratory under the mentorship of Dr. M. T Brumbach.

Michael E. Ramón (S'07–M'09–S'09–M'10–S'11) received the B.S.E. degree in electrical engineering from Princeton University, Princeton, NJ, and the M.S. degree in electrical engineering from The University of Texas, Austin. He is currently working toward the Ph.D. degree in electrical engineering at The University of Texas at Austin, where he has been funded in part by the Virginia and Ernest Cockrell, Jr., Fellowships in Engineering, the Robert N. Noyce Memorial Fellowship, and the National Science Foundation Integrative Graduate Education and

Research Traineeship Program.

After receiving the B.S.E. degree, he was at Freescale Semiconductor, Austin, TX, as a Device Engineer in transistor reliability focusing on high-*K* gate dielectrics, SOI, and strained silicon devices. His current research interests include graphene synthesis by chemical vapor deposition and graphene field-effect transistor (GFET) design and fabrication for high-frequency applications.

Mr. Ramón is a member of the Tau Beta Pi and is licensed to practice before the United States Patent and Trademark Office as a Registered Patent Agent.

**Hema C. P. Movva** received the B.Tech. degree in electrical engineering from the Indian Institute of Technology Bombay, Mumbai, India, in 2009, and the M.S.E. degree in electrical and computer engineering at The University of Texas, Austin, TX, in 2012. He is currently working toward the Ph.D. degree in electrical and computer engineering at the University of Texas, Austin, TX, under the guidance of Dr. S. K. Banerjee.

He worked at Solar Semiconductor, Inc., Hyderabad, India from 2009 to 2010 as an R&D Engineer where his research focused on crystalline silicon cell wattage loss modeling and characterization. His current research interests include transport in graphene/h-BN devices, intercalation and chemical doping of graphene.

**Rodney S. Ruoff** received the Ph.D. degree in chemical physics from the University of Illinois-Urbana, Urbana, in 1988.

He joined The University of Texas at Austin (UT-Austin), Austin, as a Cockrell Family Regents Endowed Chair in September, 2007. He was a Fulbright Fellow in 1988–1989 at the Max Planck Institute fuer Stroemungsforschung, Goettingen, Germany.

Prior to joining UT-Austin, he was the John Evans Professor of Nanoengineering in the Department of

Mechanical Engineering at Northwestern University and the Director of NU's Biologically Inspired Materials Institute from 2002 to 2007. He has coauthored 280 peer-reviewed publications devoted to chemistry, physics, materials science, mechanics, engineering, and biomedical science. He is cofounder of Graphene Energy, Inc., and the founder of Graphene Materials, LLC., and Nanode, Inc.

Dr. Ruoff is on the Editorial Board of the IEEE TRANSACTIONS ON NAN-OTECHNOLOGY; Composites, Science, and Technology; Carbon; Journal of Nanoengineering and Nanosystems. He is the Managing Editor and Editorial Board Member of the IEEE TRANSACTIONS ON NANOTECHNOLOGY. He was a Distinguished Chair Visiting Professor at Sungkyukwan University's Advanced Institute of NanoTechnology (SAINT) for several years.

Kristen N. Parrish (S'07) received the B.S. degree in electrical engineering (magna cum laude) from the Rose-Hulman Institute of Technology, Terre Haute, IN, in 2008 and the M.S. degree from the University of Texas, Austin, in 2010. She is currently working toward the Ph.D. degree at the University of Texas, where she is supported in part by fellowships from the Cockrell School of Engineering and Texas Instruments Incorporated.

She has held summer intern positions at Raytheon Technical Services Company Indianapolis, IN, and

LGS Innovations Florham Park, NJ, and Texas Instruments Incorporated, Dallas, TX. She recently completed an internship with the Kilby Labs research group at Texas Instruments Incorporated.

Ms. Parrish is a member of the Tau Beta Pi and IEEE Women in Engineering (WIE).

Sanjay K. Banerjee (F'96) received the B.Tech. degree from the Indian Institute of Technology, Kharagpur, India, in 1979, and the M.S. and Ph.D. degrees from the University of Illinois at Urbana-Champaign, Urbana-Champaign, in 1981, and 1983, respectively, all in electrical engineering.

From 1983 to 1987, he was a Technical Staff Member at Corporate Research, Development and Engineering of Texas Instruments Incorporated, where he was involved in the research on polysilicon transistors and dynamic random access trench memory cells

used by Texas Instruments in the world's first 4-Mb DRAM. From 1987 to 1990, he was an Assistant Professor and from 1990 to 1993, an Associate Professor at The University of Texas at Austin, Austin. Since 1993, he has been a Professor and is currently the Cockrell Family Regents Chair Professor of Electrical and Computer Engineering and the Director of Microelectronics Research Center, The University of Texas at Austin. He is also the Director of the SouthWest Academy of Nanoelectronics, one of three centers in the U.S. to develop a replacement for MOSFETs. He is the author or coauthor of more than 700 archival-refereed publications/talks, seven books/chapters, and holds 26 U.S. patents. He has also supervised more than 50 Ph.D. and 60 M.S. students. His research interests include ultrahigh vacuum chemical vapor deposition for silicon–germanium–carbon heterostructure MOSFETs, ultrashallow junction technology, semiconductor device modeling, nanoparticle flash memories, and nanostructures.

Dr. Banerjee was the corecipient of the Best Paper Award in the IEEE International Solid State Circuits Conference in 1986. He received the Engineering Foundation Advisory Council Halliburton Award in 1991, the Texas Atomic Energy Fellowship Award during 1990–1997, the Cullen Professorship Award during 1997–2001, and the National Science Foundation Presidential Young Investigator Award in 1988. His recent awards include the Fellow American Association for the Advancement of Science in 2007, the Hocott Research Award from University of Texas—Austin in 2007, the Fellow of Antennas and Propagation Society in 2006, the Distinguished Alumnus Award of the Illinois Institute of Technology in 2005, the Industrial Research and Development 100 Award in 2004, the ECS Callinan Award in 2003, the IEEE Millennium Medal in 2000, and the SRC Inventor Recognition Award in 2000. He was a Distinguished Lecturer for the IEEE Electron Devices Society, and the General Chair of the IEEE Device Research Conference in 2002.

**Deji Akinwande** (M'98) received the B.S. and M.S. degrees in electrical engineering and applied physics from Case Western Reserve University, Cleveland, OH, and the Ph.D. degree in electrical engineering from Stanford University, Stanford, CA, where he conducted research on the experimental synthesis, device physics, and circuit applications of carbon nanotubes and graphene. His master's research involved the design, development, and characterization of evanescent microwave probes for nondestructive imaging of materials.

He is currently an Assistant Professor at The University of Texas at Austin, Austin. He is a coinventor of a high-frequency bondwire interconnect.

Dr. Akinwande has been honored with the NSF CAREER Award, the Army Young Investigator Award, the 3M Nontenured Faculty Award. He also received the "2005 Stanford Cheesy Award" for outstanding LNA design and the Ford Foundation, Alfred P. Sloan Foundation, and Stanford DARE Fellowships.